- Robotik - Automatisierung - Informationstechnik

- Industrielle Datenverarbeitung

- FPGA Karte

- UEI - United Electronic Industries

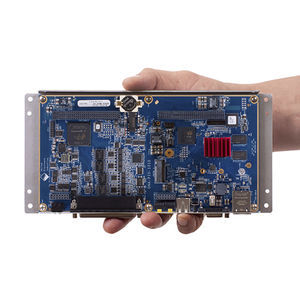

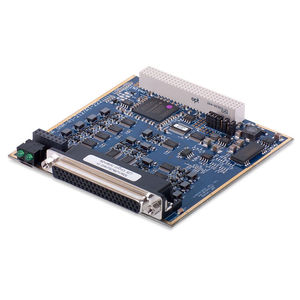

FPGA Karte DNx-PL-820 series

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Beschreibung

Die DNx-PL-820 sind benutzerprogrammierbare FPGA-Boards. Das Board ermöglicht es einem FPGA-Programmierer, die DNx-Familie und die verschiedenen von ihr unterstützten Plattformen um kundenspezifische FPGA-Funktionen zu erweitern.

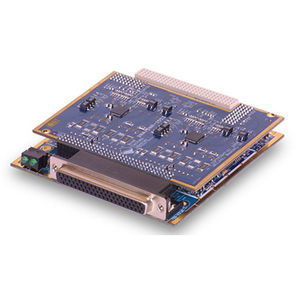

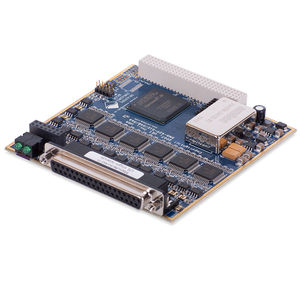

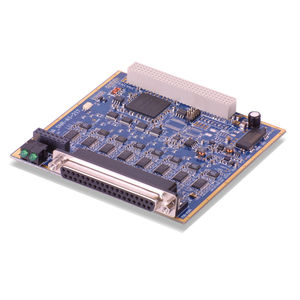

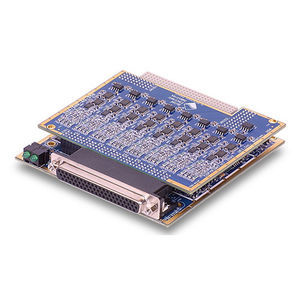

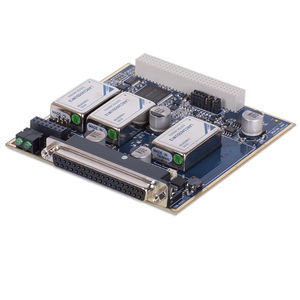

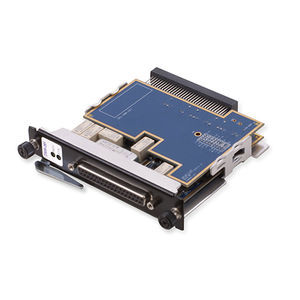

Das DNx-PL-820 ist ein Produkt mit zwei Platinen, einer Basis- und einer Tochterkarte. Die untere Karte (links in einem DNR RACK) enthält ein Cyclone II FPGA, während die obere Karte (rechts im RACK) ein MAX 10 FPGA enthält. Die Cyclone-Platine wird ausschließlich als Schnittstelle zwischen dem DNxbus und dem MAX 10 FPGA-Chip verwendet. Der MAX 10-Chip ist vom Benutzer mit den gängigen Altera-Entwicklungstools, einschließlich des eingebetteten Nios II-Prozessors, vollständig programmierbar.

Auf dem MAX 10 Board können vom Anwender entwickelte FPGA-Anwendungen installiert und ausgeführt werden. 104 GPIO-Pins sind aus dem MAX 10 FPGA herausgeführt und stehen für Verbindungen zu Benutzer-I/O zur Verfügung. 51 Bits befinden sich am I/O-Anschluss des Cyclone-Boards, während 53 am Anschluss des MAX 10-Boards zur Verfügung stehen.

Der MAX 10 verfügt über eine Vielzahl einzigartiger und leistungsfähiger Funktionen, die ihn zur idealen Wahl für ein kundenspezifisches FPGA-Target machen. Dazu gehört eine einzigartige Instant-On-Funktion, die es ermöglicht, die MAX 10-Anwendung sofort zu starten, unabhängig davon, ob der Cube oder RACKtangle seinen Bootvorgang abgeschlossen hat. Der MAX 10 unterstützt auch Benutzer- und Dualkonfigurations-FLASH, DSP-Blöcke und Nios II-Embedded-Prozessorfunktionen.

Der MAX 10-Chip kann über eine JTAG-Schnittstelle, die an den I/O-Anschluss angeschlossen ist, oder über die DNA-Backplane (viathe Cyclone-Chip) mit einem von UEI bereitgestellten Dienstprogramm programmiert werden. Mit einer Reihe von Jumpern auf der Platine kann die JTAG-Schnittstelle deaktiviert werden, wenn dies aus Sicherheitsgründen erforderlich ist.

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von UEI - United Electronic Industries anzeigenWeitere Produkte von UEI - United Electronic Industries

I/O Interfaces

Verwandte Suchbegriffe

- Schnittstellenmodul

- Schnittstellen-Kommunikationskarte

- Rack-Chassis

- Industrieschnittstellenkarte

- Multiplexer

- Serie-Schnittstellenkarte

- Industrie-Chassis

- RS232-Schnittstellenkarte

- 1U-Chassis

- 3U-Chassis

- Kompakter Chassis

- Analoge Datenerfassungskarte

- Gehärteter Chassis

- CAN-Schnittstellenkarte

- FPGA Karte

- RS-485-Schnittstellenkarte

- Chassis / 6 Steckplätze

- Mehrkanal-Schnittstellenkarte

- Ethernet-Schnittstellenkarte

- Karten-Multiplexer

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.