Programmiersoftware HDL Coder™CPLD FPGA und Mischsignal

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Programmier

- Anwendung

- CPLD FPGA und Mischsignal

Beschreibung

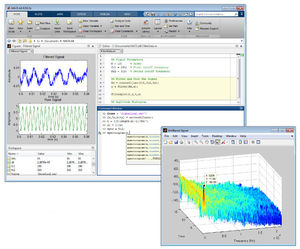

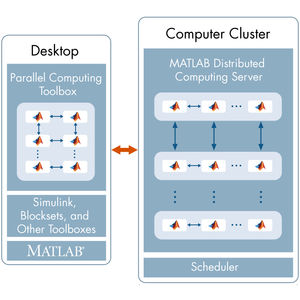

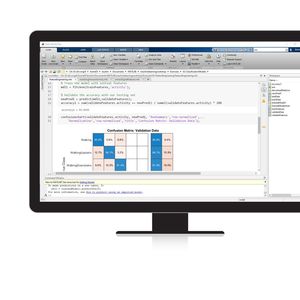

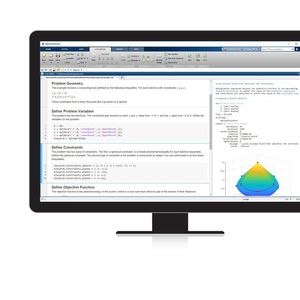

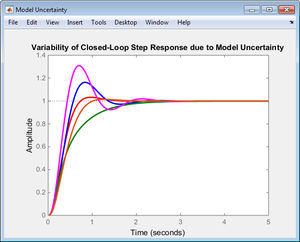

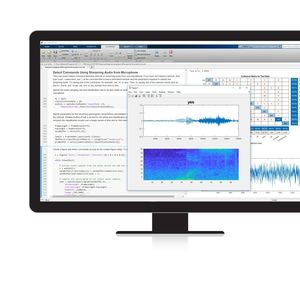

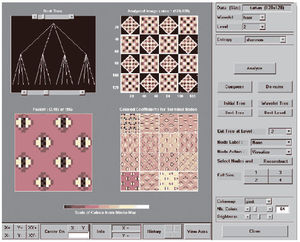

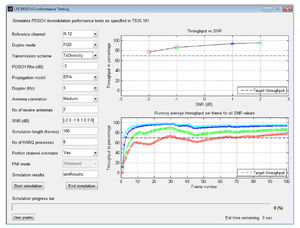

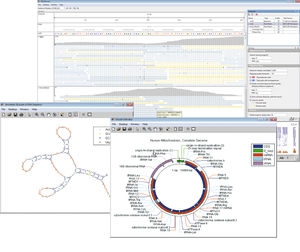

HDL Coder generiert portablen, synthetisierbaren Verilog®- und VHDL®-Code aus MATLAB®-Funktionen, Simulink®-Modellen und Stateflow®-Diagrammen. Der generierte HDL-Code kann für die FPGA-Programmierung oder für ASIC-Prototypen und ‑Entwürfe verwendet werden.

HDL Coder umfasst einen Workflow Advisor für die automatisierte Programmierung von Xilinx®-, Microsemi®- und Intel®-FPGAs. Sie können die HDL-Architektur (49:42) und -Implementierung steuern, kritische Pfade hervorheben und Schätzungen der Hardwareressourcennutzung generieren. HDL Coder ermöglicht die Rückverfolgbarkeit zwischen Ihrem Simulink-Modell und dem erzeugten Verilog- bzw. VHDL-Code und damit auch die Codeverifizierung bei Hochintegritätssystemen gemäß DO-254 und anderen Standards.

VIDEO

Kataloge

Verwandte Suchbegriffe

- Automatisierungs-Softwarelösung

- Management-Softwarelösung

- Analysesoftwarelösung

- Prozess-Softwarelösung

- Windows-Softwarelösung

- Steuerungssoftwarelösung

- Software für Architektur

- Echtzeit-Softwarelösung

- Online-Software

- Projektentwicklungs-Softwarelösung

- 3D-Softwarelösung

- Messsoftware

- Simulationssoftware

- Visualisierungs-Softwarelösung

- Programmiersoftware

- Automatisierte Softwarelösung

- Netzwerk-Softwarelösung

- Maschinensoftware

- Engineering-Software

- Software für Test

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.