Projektentwicklungssoftware Simulink Design Verifier™DiagnoseKontroll

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Projektentwicklung, Diagnose, Kontroll

Beschreibung

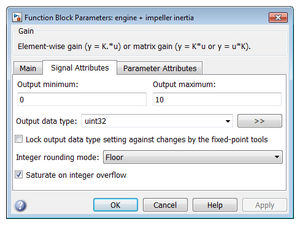

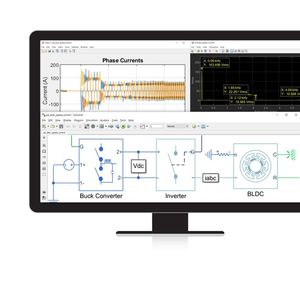

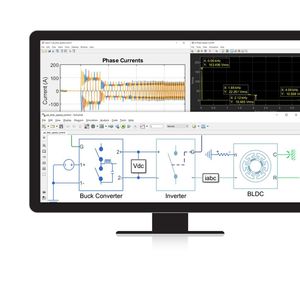

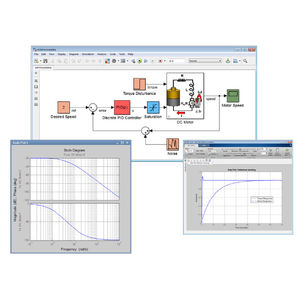

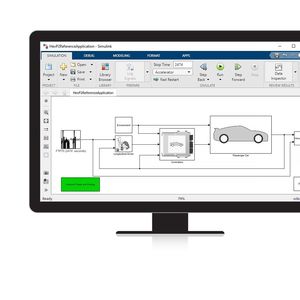

Simulink Design Verifier™ verwendet formale Methoden, um versteckte Design-Fehler in Modellen zu identifizieren. Er erkennt Blöcke im Modell, die zu Integerüberlauf, toter Logik, Array-Zugriffsverletzungen und Division durch Null führen. Er kann formal verifizieren, dass das Design funktionale Anforderungen erfüllt. Für jeden Design-Fehler und jeden Verstoß gegen Anforderungen generiert er einen Simulationstestfall für das Debugging.

Simulink Design Verifier generiert Testfälle für die Modellabdeckung und benutzerdefinierte Ziele zur Erweiterung vorhandener, auf Anforderungen basierender Testfälle. Diese Testfälle treiben Ihr Modell an, um die Abdeckungsziele Bedingung, Entscheidung, geänderte Bedingung/Entscheidung (modified condition/decision, MCDC) und benutzerdefinierte Abdeckungsziele zu erreichen. Zusätzlich zu den Abdeckungszielen können Sie benutzerdefinierte Testziele angeben, um automatisch anforderungsbasierte Testfälle zu generieren.

Die Unterstützung von Branchenstandards ist erhältlich über IEC Certification Kit (for ISO 26262 and IEC 61508) und DO Qualification Kit (for DO-178 and DO-254).

VIDEO

Kataloge

Verwandte Suchbegriffe

- Automatisierungs-Softwarelösung

- Management-Softwarelösung

- Analysesoftwarelösung

- Prozess-Softwarelösung

- Windows-Softwarelösung

- Steuerungssoftwarelösung

- Software für Architektur

- Echtzeit-Softwarelösung

- Online-Software

- Projektentwicklungs-Softwarelösung

- 3D-Softwarelösung

- Messsoftware

- Simulationssoftware

- Visualisierungs-Softwarelösung

- Programmiersoftware

- Automatisierte Softwarelösung

- Netzwerk-Softwarelösung

- Maschinensoftware

- Engineering-Software

- Software für Test

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.