Schnittstellen-Software Package SignoffSteuerungProjektentwicklungKontroll

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Schnittstellen, Steuerung, Projektentwicklung, Kontroll

- Anwendung

- Prozess, Auslauf

- Typ

- automatisiert, 2D-3D

Beschreibung

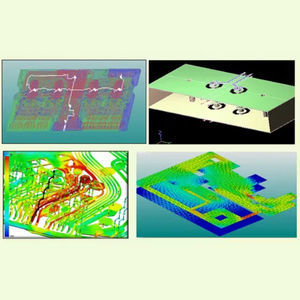

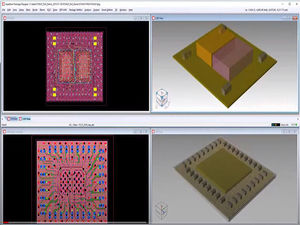

Entwurfsprüfung von Baugruppen mit mehreren Chips und Substraten durch Identifizierung von Geometrien pro Schicht und Chipplatzierung in der Baugruppe. DRC und LVS werden an den Schnittstellengeometrien zwischen den Chips mit Unterstützung für Chips aus mehreren Prozessen durchgeführt.

Foundry/OSAT-gesteuerte Substratverifizierung

Wenn Leistung und Time-to-Market die potenzielle Rentabilität steuern, ermöglicht die Verwendung von Calibre nmDRC für Ihre physikalische Verifikation den Erfolg. Calibre wird ständig weiterentwickelt, um den Anforderungen schrumpfender Geometrien und komplexer Fertigungsmethoden gerecht zu werden, und die Regelwerke von Calibre haben sich schon lange bewährt, bevor Sie sie benötigen.

Linksverschiebung im Design Fabrication DRC

Verpackungslösungen der nächsten Generation erfordern eine bewährte, automatisierte Freigabe für die physikalische, elektrische, thermische und fertigungstechnische Leistung innerhalb einer einzigen Umgebung, die es den Designern ermöglicht, all diese Prozesse in einem effizienten, wiederholbaren und automatisierten Ablauf zu verwalten. Durch die Verwendung von Calibre und HyperLynx für die Verifizierung können die Entwickler Probleme vor der endgültigen Freigabe erkennen und lösen.

Regelgesteuerte Foundry/OSAT-Substrat-Metall-Verifizierung

Die gleichungsbasierte DRC-Technologie (eqDRC) bietet dem Benutzer Erweiterungsmöglichkeiten und schnelle Laufzeiten für eine Vielzahl komplexer Design- und Prozessinteraktionen. eqDRC ermöglicht präzise und genaue Charakterisierungen komplexer, multivariabler und nicht-Manhattan-Geometrien sowie 2D/3D-Interaktionen, die sich direkt auf die Leistung und/oder Herstellbarkeit auswirken.

Signoff-Verifizierung von 2,5/3D gestapelten Die-Baugruppen

Bietet eine vollständige Design-Verifizierung von gestapelten Die-Baugruppen.

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von SIEMENS EDA anzeigenVerwandte Suchbegriffe

- Automatisierungs-Softwarelösung

- Management-Softwarelösung

- Analysesoftwarelösung

- Prozess-Softwarelösung

- Windows-Softwarelösung

- Steuerungssoftwarelösung

- Software für Architektur

- Echtzeit-Softwarelösung

- Online-Software

- Projektentwicklungs-Softwarelösung

- 3D-Softwarelösung

- Schnittstellen-Software

- Messsoftware

- Software für Industrieanwendungen

- Qualitätssoftware

- Simulationssoftware

- Visualisierungs-Softwarelösung

- Automatisierte Softwarelösung

- Entwicklungssoftware

- Netzwerk-Softwarelösung

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.