Management-Software Xpedition Substrate IntegratorVisualisierungProjektentwicklungPlanung

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Management, Visualisierung, Projektentwicklung, Planung, Optimierung, Kontroll, Konnektivität, Prototyping

- Anwendung

- Prozess

- Typ

- 3D

Beschreibung

Heterogene und homogene 2,5/3D-IC-Gehäuse-Konnektivität Planung, Prototyping von Baugruppen und Co-Optimierung der Systemtechnologie.

2.5/3D IC-Gehäuse Planung & Prototyping

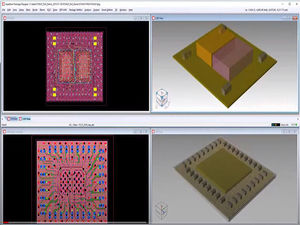

Frühzeitiges Prototyping und Exploration ermöglicht es Ingenieuren, verschiedene ASIC/Chiplet-, Interposer-, Gehäuse- und PCB-Integrationsszenarien zu evaluieren, um vor der detaillierten physischen Implementierung die Gesamt-PPA-, Bauteilgrößen-, Routing- und Kostenziele zu erreichen.

Hauptmerkmale von Substrate Integrator

Vollständiger oder teilweiser Import von Schaltplänen

Die logische Konnektivität von IC-Gehäusen kann mit Hilfe von vollständigen oder teilweisen grafischen Schaltplänen erstellt werden. Dies ist nützlich für Designs mit einer hohen Anzahl von Bauteilen, wie z. B. SiP-Module, und/oder für die Wiederverwendung/Retargeting von früheren Designs.

Management der Gehäuse-Konnektivität auf Systemebene

Systemkonnektivitätsmanagement, Visualisierung und logische Verifizierung auf Systemebene von IC-Gehäusedesigns mit mehreren Bauelementen, Komponenten und Substraten.

Aggregation von Die, Chiplets und Substraten

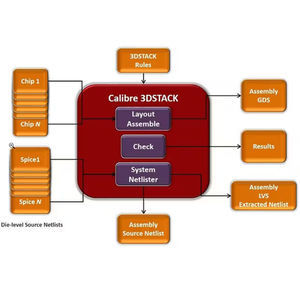

Xpedition Substrate Integrator integriert Die, Chiplets und Interposer von verschiedenen Prozessknoten und Lieferanten. Es werden mehrere Formate unterstützt, darunter LEF/DEF, GDS, AIF und CSV/TXT. Hierarchische virtuelle Die-Modelle unterstützen bidirektionale ECO-Änderungen von Objekten während der Konstruktion/Optimierung.

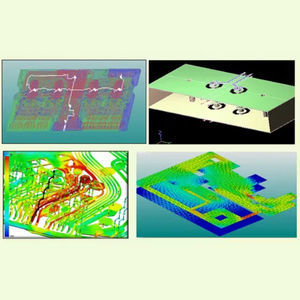

Silizium-Gehäuse-PCB-Cross-Substrat-Ko-Optimierung

Die substratübergreifende Planung und Co-Optimierung verbessert die Vorhersagbarkeit während der Implementierung erheblich, da Probleme gefunden und behoben werden können, bevor sie sich in einem späten Stadium zu Überraschungen entwickeln. Eine Systemperspektive mit substratübergreifender Sichtbarkeit verbessert die Kommunikation und Koordination durch unmittelbare Rückmeldung zu Entscheidungen, die normalerweise auf der Basis einzelner Substrate getroffen werden.

---

Kataloge

Xpedition Substrate Integrator

4 Seiten

Verwandte Suchbegriffe

- Automatisierungs-Softwarelösung

- Management-Softwarelösung

- Analysesoftwarelösung

- Prozess-Softwarelösung

- Windows-Softwarelösung

- Steuerungssoftwarelösung

- Software für Architektur

- Echtzeit-Softwarelösung

- Online-Software

- Projektentwicklungs-Softwarelösung

- 3D-Softwarelösung

- Schnittstellen-Software

- Messsoftware

- Software für Industrieanwendungen

- Qualitätssoftware

- Simulationssoftware

- Visualisierungs-Softwarelösung

- Automatisierte Softwarelösung

- Entwicklungssoftware

- Netzwerk-Softwarelösung

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.