Analysesoftware Solido Design EnvironmentEngineeringProjektentwicklungKontroll

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Analyse, Engineering, Projektentwicklung, Kontroll, Debug

- Anwendung

- Prozess

- Weitere Eigenschaften

- für gewerbliche Nutzung

Beschreibung

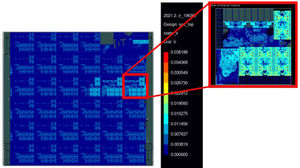

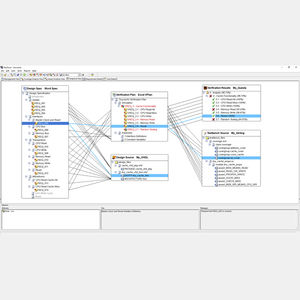

Umfassende KI-gestützte Designumgebung für die nominale und variantenabhängige Verifizierung von Speicher-, Standardzellen- und kundenspezifischen Analog-/RF-IC-Designs

Solido Design-Umgebung

Eine umfassende KI-gestützte Design-Umgebung

für alle Design- und Verifikationsaufgaben auf SPICE-Ebene und eine einheitliche Lösung

für Nominal- und Variationsanalysen. Wird von Tausenden von Designern für die Produktion der wettbewerbsfähigsten

produkte in den Bereichen HP-Computing, KI, IoT, Automotive und mobile Anwendungen.

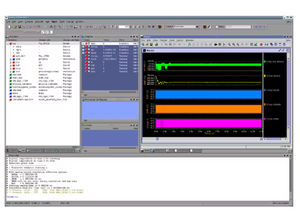

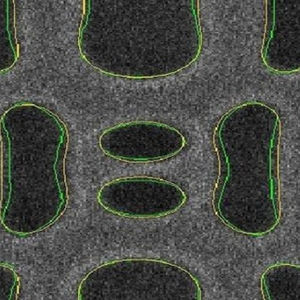

Brute-Force-genaue Signoff-Variation 1000x schneller

Um Größenordnungen schneller als

brute-Force-Simulation

Vollständige Überprüfung der Abdeckung über PVTs

und Monte Carlo

Brute-Force Monte Carlo und SPICE

genaue Verifizierung im hohen Sigma-Bereich

Variationsbewusste Entwurfsempfindlichkeit,

fehlersuche und Optimierung

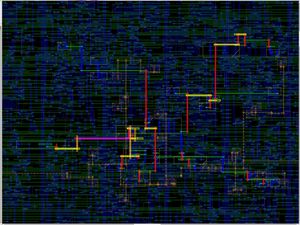

Umfassende Entwurfsumgebung

zur Steigerung der Entwicklungseffizienz

Erheblich reduzierte Dokumentation

zeit/Aufwand

Identifiziert Schwachstellen im Entwurf

die zuvor unerkennbar waren

Einfach zu verwenden und einzusetzen

Intuitive GUI für interaktiven Entwurf

und Analyse

GUI- oder Batch-Modus

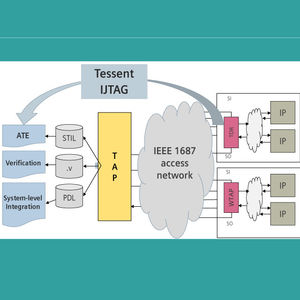

Arbeitet mit allen Prozesstechnologien

Integriert in führende Entwurfs

umgebungen

Unterstützt die meisten kommerziellen und internen

SPICE-Simulatoren

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von SIEMENS EDA anzeigenVerwandte Suchbegriffe

- Automatisierungs-Softwarelösung

- Management-Softwarelösung

- Analysesoftwarelösung

- Prozess-Softwarelösung

- Windows-Softwarelösung

- Steuerungssoftwarelösung

- Software für Architektur

- Echtzeit-Softwarelösung

- Online-Software

- Projektentwicklungs-Softwarelösung

- 3D-Softwarelösung

- Schnittstellen-Software

- Messsoftware

- Software für Industrieanwendungen

- Qualitätssoftware

- Simulationssoftware

- Visualisierungs-Softwarelösung

- Automatisierte Softwarelösung

- Entwicklungssoftware

- Netzwerk-Softwarelösung

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.