Qualitätssoftware Catapult® SteuerungProjektentwicklungOptimierung

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Qualität, Steuerung, Projektentwicklung, Optimierung, Kontroll, Synthese

- Anwendung

- Prozess, Auslauf, CPLD FPGA und Mischsignal

Beschreibung

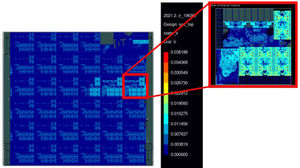

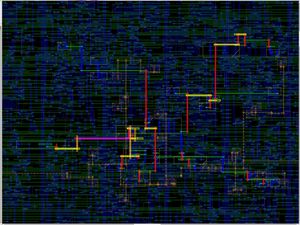

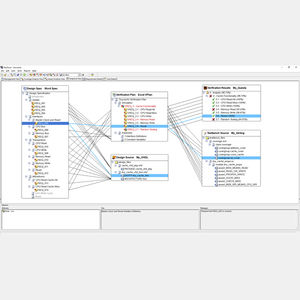

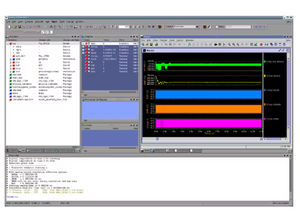

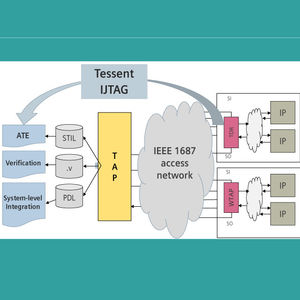

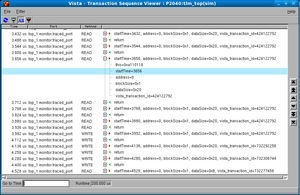

Catapult verfügt über das breiteste Portfolio an Hardware-Design-Lösungen für C++ und SystemC-basierte High-Level-Synthese (HLS). Catapults physikbewusster Multi-VT-Modus mit Low-Power-Schätzung und -Optimierung sowie eine Reihe führender Verifikationslösungen machen Catapult HLS zu mehr als nur "C to RTL".

Catapult-Kunden diskutieren über den Einsatz von HLS in der realen Welt

In den letzten Jahren hat sich der Einsatz von HLS für das Chipdesign aufgrund der zunehmenden Komplexität von Design und Verifikation sowie des Zeitdrucks bei der Markteinführung explosionsartig entwickelt. Catapult HLS ermöglicht es Entwicklern, ihre Chips schneller auf den Markt zu bringen, indem es den gesamten Design- und Verifikationsablauf verkürzt.

Catapult High-Level-Synthese-Lösungen

Die High-Level-Synthese-Lösungen von Catapult bieten C++- und SystemC-Sprachunterstützung, FPGA- und ASIC-Unabhängigkeit, ASIC-Leistungsabschätzung und -Optimierung sowie die neueste physikalisch bewusste Multi-VT-Flächen- und Leistungsoptimierung, um Ihre Designs zu verbessern.

Catapult High-Level Verification Lösungen

Beschleunigen Sie Ihren High-Level-Verification (HLV)-Fluss mit bekannten und bewährten Methoden unter Verwendung der Catapult HLV-Plattform. Reduzieren Sie die Gesamtdurchlaufzeit und die Kosten für die SoC-Verifikation um bis zu 80 %, indem Sie High-Level Design Checking, Code/Functional Coverage und statische sowie formale Methoden einsetzen.

Catapult High-Level-Synthese

Finden Sie heraus, wie die Catapult High-Level-Synthese- und Verifikationsplattform es Ihnen ermöglicht, mehr zu tun und es besser zu tun. Erfahren Sie mehr über AI/ML, Deep Learning, Computer Vision, Kommunikation, Video und mehr. Die High-Level-Synthese- und Verifikationstools (HLS & HLV) von Siemens verschaffen Ihnen den nötigen Wettbewerbsvorteil.

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von SIEMENS EDA anzeigenVerwandte Suchbegriffe

- Automatisierungs-Softwarelösung

- Management-Softwarelösung

- Analysesoftwarelösung

- Prozess-Softwarelösung

- Windows-Softwarelösung

- Steuerungssoftwarelösung

- Software für Architektur

- Echtzeit-Softwarelösung

- Online-Software

- Projektentwicklungs-Softwarelösung

- 3D-Softwarelösung

- Schnittstellen-Software

- Messsoftware

- Software für Industrieanwendungen

- Qualitätssoftware

- Simulationssoftware

- Visualisierungs-Softwarelösung

- Automatisierte Softwarelösung

- Entwicklungssoftware

- Netzwerk-Softwarelösung

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.