- Elektrotechnik - Elektronik

- Elektronisches Bauteil

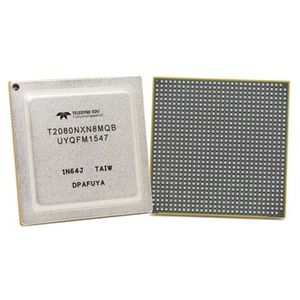

- 32-Bit-Mikrocontroller

- e2v scientific instruments

32-Bit-Mikrocontroller TS68EN360

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Typ

- 32-Bit

Beschreibung

Eigenschaften

• CPU32+-Prozessor (4,5 MIPSS bei 25 MHZ)

– 32-Bit-Version des Kernes CPU32 (völlig - kompatibel mit dem CPU32)

– Hintergrund prüfen Modus aus

– Byte-versetztes Wenden

• Bis 32-Bit-Datenbus (dynamisches Bus-Bearbeiten für 8 und 16 Bits)

• Bis 32 Adreßlinien (28 mindestens immer verfügbar)

• Kompletter statischer Entwurf (0 - 25 MHZ-Operation)

• Sklaven-Mode, zum von CPU32+ zu sperren (erlaubt Gebrauch mit externen Prozessoren)

– Mehrfaches QUICCs kann einen System-BUS (einen Meister) teilen

– Modus des Begleiter-TS68040 lässt QUICC ein Chip des Begleiter-TS68040 und ein intelligentes Peripherie sein

(22 MIPSS bei 25 MHZ)

– Peripheriegerät von TSPC603e (sehen Sie DC415-/Danmerkung)

• Vier universelle Timer

– Superset von Timern MC68302

– Vier 16-Bit-Timer oder zwei 32-Bit-Timer

– Tor-Modus kann die Zählung aktivieren

• Zwei unabhängiges DMAs (IDMAs)

• Integrations-Modul (SIM60)

• Kommunikationsprozessor-Modul (Cpm)

• Vier Baud Rate Generators

• Vier SCCs (Ethernet/IEEE 802,3 optional auf SCC1-Full 10 Mbps Unterstützung)

• Zwei SMC

• VCC = +5V-± 5%

• fmax = 25 MHZ und 33 MHZ

• Militärtemperaturspanne: -55°C < TC < +125°C

• PD = 1.4W bei 25 MHZ; 5.25V

2W bei 33 MHZ; 5.25V

Beschreibung

Die integrierte Datenübertragungssteuerung des Viererkabel-TS68EN360 (QUICC™) ist ein integrierter Mikroprozessor des vielseitigen Einchips

und Zusatzkombination, die in einer Vielzahl von Prüferanwendungen verwendet werden kann. Sie übertrifft besonders in den Kommunikationen

Tätigkeiten. Das QUICC (schnell ausgesprochen „") kann als zukünftiges TS68302 mit höherer Leistung in allen beschrieben werden

Bereiche der Gerätoperation, der erhöhten Flexibilität, der bedeutenden Erweiterungen in der Fähigkeit und der höheren Integration.

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von e2v scientific instruments anzeigenWeitere Produkte von e2v scientific instruments

Semiconductors

Verwandte Suchbegriffe

- Signalverstärker

- Transceiver-Modul

- RF-Transceiver

- Rauscharmer Verstärker

- Mikrocontroller

- CMOS-Bildsensor

- RF-Verstärker

- Infrarot-Bildsensor

- Programmierbarer Wandler IC

- Wandler IC / ADC

- Transceiver mit geringer Leistung

- Wandler IC / für hohen Durchsatz

- VIS-Bildsensor

- 32-Bit-Mikrocontroller

- Bildsensor mit hoher Drehzahl

- Wandler IC / DAC

- Mehrweg Wandler IC

- Isolationsverstärker

- Hochempfindlich-Bildsensor

- Nahinfrarot-Bildsensor

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.