- Robotik - Automatisierung - Informationstechnik

- Industrielle Datenverarbeitung

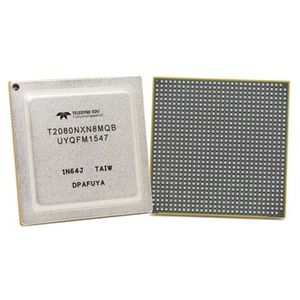

- Prozessor

- e2v scientific instruments

Prozessor PC8540

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Beschreibung

Eigenschaften

• Eingebetteter E-kompatibler Kern verfügbare bis 833 MHZ des Buch-e500

– 32-Bit, Doppel-Frage, Superscalar, Sieben-Stadium Rohrleitung

– 1850 MIPSS bei 800 MHZ (Est. Dhrystone 2,1)

– 32 KBs L1-Daten und 32 Anweisungs-Pufferspeicher KBs L1 mit der Linie, die Unterstützung zuschließt

– 256 KB-Auf-Chip L2 Pufferspeicher mit direkter aufgezeichneter Fähigkeit

– Erhöhte Hardware und Software prüfen Unterstützung aus

– Speicherverwaltungs-Einheit (MMU)

– SIMD-Erweiterung mit einfache Genauigkeits-Gleitkomma

• Zwei TSECs, das 10/100/1000 Mbps-Ethernet stützt (IEEE® 802,3, 802.3u, 802.3x,

802.3z und 802,3 Wechselstrom-konform) mit zwei GMII-/TBI/RGMIIschnittstellen

• 166 MHZ, 64-Bit, 2.5V Input/Output, Gedächtnis-Prüfer DDR SDRAM mit voller ECC-Unterstützung

• 500 MHZ, 8-Bit, LVDS Input/Output, RapidIO-Prüfer

• 133 MHZ, 64-Bit, 3.3V Input/Output, PCI-X 1.0a/PCI 2,2 Bus-Prüfer

• 166 MHZ, 32-Bit, 3.3V Input/Output, local bus mit Gedächtnis-Prüfer

• Integrierter VierkanaldMA-Controller

• Unterbrechungssteuerung

• Test-Zugangs-Hafen IEEE 1149,1 JTAG

• Spannung des Kern-1.2V mit Input/Output 3.3V und 2.5V

Beschreibung

Das PC8540 enthält einen PowerPC®-Prozessorkern. Das PC8540 integriert einen Prozessor, der das PowerPC einführt

Architektur mit der Systemlogik erfordert für Vernetzung, Lagerung und universelle eingebettete Anwendungen. Für Funktions

Eigenschaften des Prozessors, beziehen sich das auf PC8540 integrierten Prozessor-einleitendes Handbuch.

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von e2v scientific instruments anzeigenWeitere Produkte von e2v scientific instruments

Semiconductors

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.