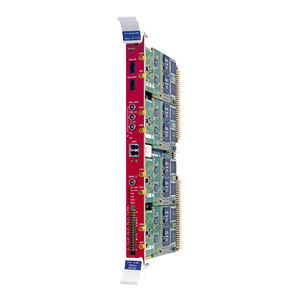

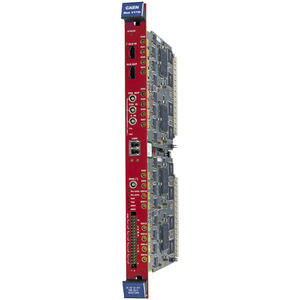

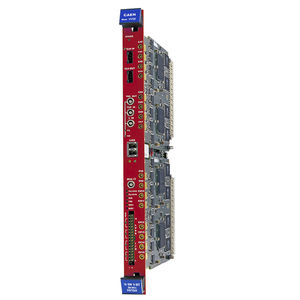

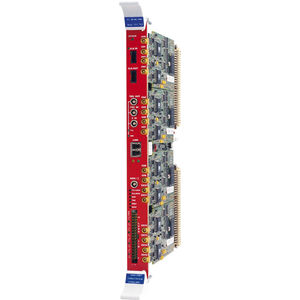

Digitalisierer / bis 5 GS/s V174232 Kanäle12-BitPCIe

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Möchten Sie direkt kaufen?

Besuchen Sie unseren Shop.

Eigenschaften

- Geschwindigkeit

- bis 5 GS/s

- Anzahl Kanäle

- 32 Kanäle

- Merkmal

- 12-Bit, PCIe, VME

Beschreibung

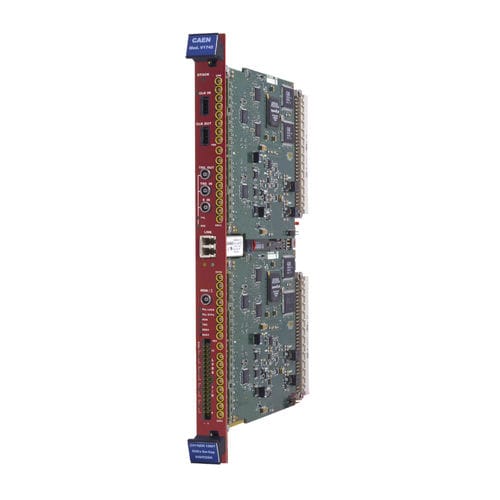

Das CAEN Mod. V1742 ist ein 1 Einheit breites VME 6U Modul, das 32+2 Kanal 12 Bit 5 GS/s Switched Capacitor Digitizer Sektionen enthält. Der Eingangsdynamikbereich beträgt 1 Vss an unsymmetrischen MCX-Koaxialanschlüssen (16-Bit-DAC auf jedem Kanal zur Steuerung des DC-Offsets).

Der Digitalisierer basiert auf dem Switched Capacitor Array DRS4 Chip (Domino Ring Sampler). Diese Technologie beruht auf einer Reihe von 1024 Kondensatoren (Analogspeicher), in denen das analoge Eingangssignal kontinuierlich kreisförmig abgetastet wird.

Die Abtastfrequenz beträgt standardmäßig 5 GHz und kann auf 2,5 GHz, 1 GHz und 750 MHz programmiert werden. Die Analog-Digital-Wandlung erfolgt nicht gleichzeitig mit der Abtastphase des Chips, sondern beginnt, sobald die Triggerbedingung erfüllt ist, was zu einer Totzeit von 110 μs führt, wenn nur die Analogeingänge digitalisiert werden, und 181 μs, wenn auch der schnelle Trigger TRn digitalisiert wird. Wenn der Trigger die Abtastung des DRS4-Chips stoppt (Haltephase), wird der analoge Speicherpuffer eingefroren, und der Zelleninhalt wird dem 12-Bit-ADC für die digitale Umwandlung zur Verfügung gestellt.

Der digitale Speicher ermöglicht die Speicherung nachfolgender Ereignisse, auch wenn die Auslesung noch nicht begonnen hat. Da die digitalen Speicherpuffer wie FIFOs arbeiten, hat die Ausleseaktivität von VME oder Optical Link keinen Einfluss auf die Schreiboperationen der nachfolgenden Ereignisse.

Die verfügbaren Triggerquellen sind:

- Externer Trigger, Trigger am TRG-IN-Anschluss, gemeinsam für alle aktivierten Gruppen.

- Fast (Low Latency) Local Trigger, Trigger an den Anschlüssen TR0 und TR1, gemeinsam für Paare von Gruppen. Dieser Modus wird als "Fast" oder "Low Latency" bezeichnet, da die Trigger-Latenzzeit zum Halten des DRS4 im Vergleich zum externen Trigger reduziert ist.

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von CAEN Spa anzeigenVerwandte Suchbegriffe

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.