Analysesoftware PathFinder-SCSimulationProjektentwicklungPlanung

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Analyse, Simulation, Projektentwicklung, Planung

Beschreibung

Ansys PathFinder-SC ist eine leistungsstarke Lösung, die Sie bei der Planung, Verifizierung und Signierung von IP- und Full-Chip-SoC-Designs im Hinblick auf Integrität und Robustheit gegenüber elektrostatischer Entladung (ESD) unterstützt.

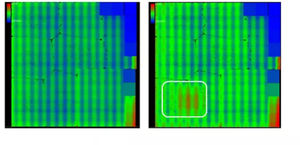

Full-Chip Layout Level ESD Signoff Lösung für SOC IP

Ansys PathFinder-SC identifiziert und isoliert die Grundursachen von Designproblemen, die zu einem Ausfall des Chips führen können, und zwar aufgrund des Charged-Device-Modells (CDM), des Human Body Models (HBM) oder anderer ESD-Ereignisse. Die leistungsstarke, Cloud-native Architektur kann Tausende von Rechenkernen für eine schnelle Bearbeitung des gesamten Chips nutzen. PathFinder-SC ist von großen Foundries für Widerstands- und Stromdichteprüfungen zur ESD-Abnahme zertifiziert.

Integriert mit Ansys RedHawk-SC™ und Ansys Totem™

Ausgänge Chip ESD Compact Model (CECM)

Schnelle Spezifikationen

Die integrierte Datenmodellierungs-, Extraktions- und Transientensimulations-Engine von PathFinder-SC ist eine End-to-End-Lösung für die ESD-Verifikation. Das in einem Durchgang zu verwendende Modell liest Designformate nach Industriestandard, stellt ESD-Regeln auf, extrahiert die RCs für das Stromversorgungsnetz und führt ESD-Simulationen durch, um die Ursachen zu analysieren und Feedback zur Behebung und Optimierung zu liefern - alles in einem einzigen Tool.

CDM & HBM-Abdeckung

P2P-Widerstandsprüfungen

Stromdichte- und IR-Prüfungen

Unterstützung von GDS und Digital Flow

Cloud-native Architektur

Analysieren Sie mehrere Domänen in einem einzigen Durchlauf

Verarbeitet Snap-back ESD

Kapazität von mehr als 100 Millionen Instanzen

Layout-GUI für Debugging

Kompaktes ESD-Modell für IP

---

VIDEO

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von ANSYS anzeigenMessen

Sie können diesen Hersteller auf den folgenden Messen antreffen

Verwandte Suchbegriffe

- ANSYS Automatisierungssoftware

- ANSYS Management-Software

- ANSYS Analysesoftware

- ANSYS Prozess-Software

- ANSYS Steuerungssoftware

- ANSYS CAD-Software

- Echtzeit-Softwarelösung

- Online-Software

- ANSYS Projektentwicklungssoftware

- ANSYS 3D-Software

- Überwachungssoftwarelösung

- Schnittstellen-Software

- Messsoftware

- ANSYS Industrie-Software

- ANSYS Qualitätssoftware

- ANSYS Simulationssoftware

- Visualisierungs-Softwarelösung

- ANSYS automatisierte Software

- ANSYS Entwicklungssoftware

- Netzwerk-Softwarelösung

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.